特集記事

ALD(原子層堆積)超薄膜による 絶縁コーティング及びウィスカ防止への展開

PICOSUN JAPAN(株) 八尋 大輔

1. 緒言

半導体製造工程は実装工程とは異なると一般的に考えられている。

たとえば要求されるクリーン度、品質、歩留まりは確 かに別世界であり、そのため使われる装置や薬品なども異なるスペックのものが必要となる。

しかし回路の微細化・部品の小型化が進展し、またいっぽうではデバイスのモジュール化が進むにつれ、一部ではその境界はかつてほど明瞭ではなくなりつつある。

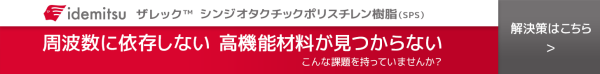

半導体製造工程の技術であるALD(原子層堆積)も、実装工程に近いところでも応用可能なことが知られて おり、本稿では特に、絶縁性、並びに、ウィスカ(図1)の防止に 焦点を当てて詳述する。

図1 種々のウィスカSEM像(: a)フィラメント状、(b)ノジュール状、(c)特殊形状、(d)らせん状、(e)よじれ状

2. ALD技術の概略

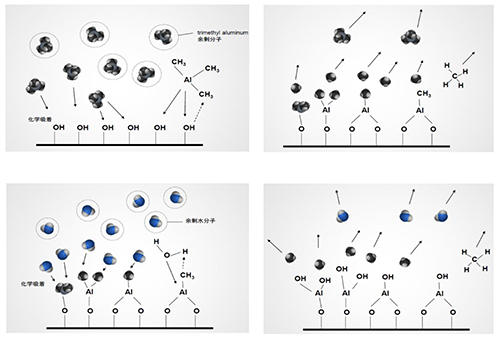

ALD 成膜(図2)の特徴については本誌でも何度か述べているが、以下の通り再掲する。

•膜質が化学量論比に近く非常に緻密であり、ピンホールフリー

•素地への密着性が高い

•複雑な 3D形状物やナノスケール表面(高ARトレンチ・ナノポアなど)へも均一に成膜できる

•再現性の高いプロセスとして膜厚を厳密にコントロールできる

•比較的低温での成膜が可能で、基板へのダメージを低減できる

スパッタや CVDと同様にドライプロセスであるが、上記の特徴により、アプリケーションによっては他の成膜方法では代替できない。

たとえば今日のAR100を超えるDRAMセルキャパシタ表面への成膜や、MEMSなどの複雑構造内部壁面へのコンフォーマルな成膜はALD以外の技術では事実上不可能である。

ALDプロセス装置は大きく、原料ライン・反応室・排気ラインに分けられる。

成膜反応は以下のように進む。

①プリカーサ(前駆体)と呼ばれるガス原料の一種目(通常2種使われる)をソースラインから反応チャンバへ移送

②反応チャンバにて、プリカーサ①が基板表面に吸着。

吸着エネルギーは一般的に熱だが、成膜材料によってはプラズマも使われる

③吸着反応での副生成物と余剰のプリカーサを排気

④二種目のプリカーサをソースラインから反応チャンバへ移送

⑤プリカーサ②が、プロセス②で基板表面に吸着したプリカーサ①に吸着し化合物を作る

⑥吸着反応での副生成物と余剰のプリカーサを排気

上記①〜⑥を繰り返すことで膜厚を増やしていくことができる。

図2 ALDプロセス図解

ALDに使用されるプリカーサ分子は基板表面のみ、または対応するプリカーサとのみ反応するため、厳密に分子層一層ずつを積み上げていくことが可能となる。

またプリカーサを交互にチャンバ内に入れることで余分な反応をさせず、化学量論比に近い膜が成膜される。

そのため絶縁性・バリア性などの膜性能が他の成膜方法と比較して高いのが特徴である。

3. ALD膜の絶縁性

ALD技術は1974年に発明されたが、他の成膜方法と比較するとスループットが見劣りするため、長らく生産用途には不向きとされてきた。

ブレイクスルーは発明から30年以上たった2007年にインテルが high-k 絶縁膜にALDを採用してからである。

従って、ALDの生産用アプリケーションとしては、絶縁膜は比較的歴史があるといえる。

今日、絶縁膜としては浸漬・スプレーコーターやエアゾールなどのウェット処理が多い。

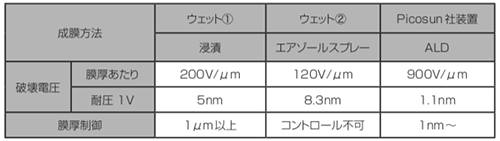

しかし[表1]に示す通り、ALDはそれらの膜を絶縁性(破壊電圧)においてはるかにしのぐ。

表1 一般的な絶縁膜とALDの比較

また重要なのは、膜厚をナノメーターレベルまで薄くしても均一に成膜できるということである。

ウェットではミクロンレベルでないと性能が発揮できない、もしくはそもそも膜厚のコントロールがほとんどできない。

微細化されたパッケージ内の占有面積を極限まで切り詰める必要のある最先端のエレクトロニクスモジュールでは致命的になり得る。

ALDは成膜に時間がかかり、そのためスループットが制限されることがデメリットとしてしばしば言及される。

しかし、ここで述べているような極小モジュールの場合、要求される絶縁性はそれほど高くなく、数Vで十分というケースも多い。

その場合、ALD膜では10nm 程度の膜厚で性能を満たす。

ALDプロセスでは、成膜時間は単純に膜厚に比例するため、材料にもよるが10nmであれば数分で成膜を終えることも可能である。

また、複雑形状物表面へもコンフォーマルかつ均一に成膜できることも強みである。

このため、ある程度実装した後にモジュール全体を絶縁することも可能である。

一般的な酸化物ALD膜材料はセラミックであるため耐熱性も高いが、はんだ付け工程においてはフラックスで除去されるため、実装前のデバイスへの成膜にも適用可能と考えられる。

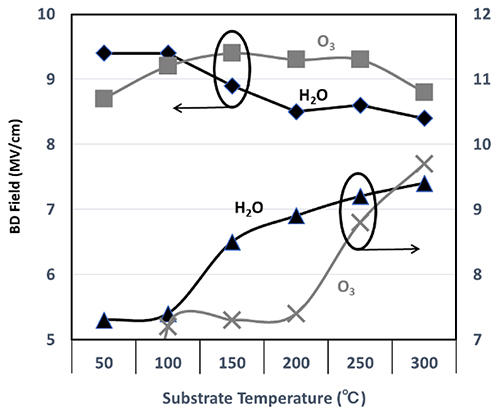

なお、膜特性は同じ材質でも成膜条件(温度、プリカーサなど)によって変わる。

参考までに、酸化剤と成膜温度の違いで電気特性がどのように変動するかを(図3)に示す。

図3 酸化剤による成膜温度ごとの電気特性

4. ALDによるウィスカ防止

すず合金によるウィスカは、1940年代からエレクトロニクスの世界では知られていた。

鉛の添加によって防げることから、鉛はんだが主流であった80〜90年代には問題とされていなかったが、RoHS規制対応のために鉛フリーはんだが使われはじめた2000年前後にクローズアップされることとなった。

ウィスカは、はんだ・めっきなどのすず薄膜表面に発生する細線状の結晶成長で、バルク状態のすず表面には発生しにくいため、薄膜内部の局所的な応力勾配が駆動力であると考えられている。

ウィスカは金属結晶であり導電性があるため、端子・基板上に付着することで電気的短絡を起こす恐れがある。

したがって、ウィスカを防止することは、電子機器の信頼性を向上させる上で必要不可欠であり、様々な取り組みが行われている。

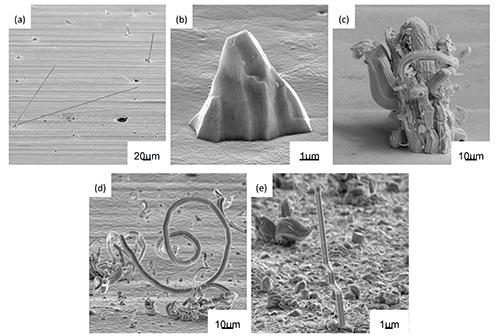

Picosun社はプリント基板アセンブリにALDコーティ ングを施すことにより、すずウィスカを防止する研究をESA(European Space Agency、欧州宇宙機関)と共同で行った。

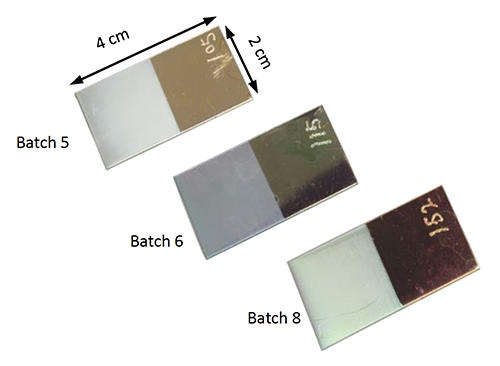

銅板上に厚さ2μmのSn-Cu電気めっきされたものを試験片として使用した(図4)。

図4 試験片写真

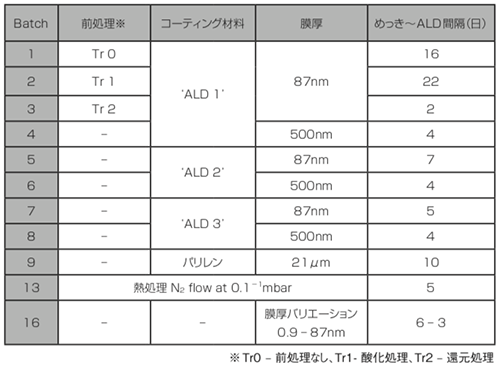

その後、[表2]に示す処理を行い、室温にて8〜12か月経過後にウィスカの発生を観察(任意の20個所での発生数平均)した。

表2 試験工程水準表

その際、バッチ1、2を除いて、ALD処理をしない以外はまったく同一のプロセスで作成したコントロールサンプルを用意し比較した。

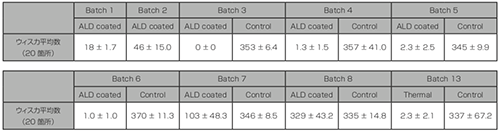

結果を[表3]に示し、簡単に結論を下記する。

表3 ウィスカ平均観察数

•ALDコーティングされていないサンプルからは〜350程度のフィラメント状ウィスカ(図1参照)の発生が見られた

•バッチ7・8を除き、ALDコーティングされたサンプルでは、ウィスカの大幅な低減が見られた(バッチ3では観察数ゼロ)

•発生数だけでなく、ウィスカ長さについても差が見られた(バッチ3〜6 のALDコート品では50〜75μm、未コート品では100〜500μm)

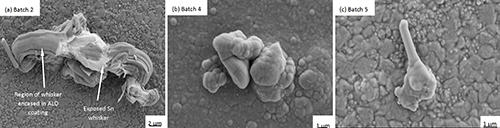

•SEM観察によると、ALDコート品で発生したウィスカは、ほとんどがALDコーティングされている(図5参照)。

図5 ALD工程後、酸化膜中に封止されたウィスカ (a)一部クラックの入った膜中のウィスカ (b()c)完全にコートされたウィスカ

すなわち、ALD処理前からすでに発生していたウィスカであると考えられる。

5. 結言

本稿で述べたように、電子デバイスパッケージやプリント基板アセンブリにおいてもALDの用途は広がっている。

ウィスカ対策に関しては、紙面の都合上内容を大幅に割愛せざるを得なかったため、興味のある読者は是非、末尾に記載する原著にあたってほしい。

また、以前メディカルデバイスへのALDについての寄稿で述べたように、気密封止性・耐腐食性などの特性も応用可能である。

実装工程においても微細化がますます進んでいく昨今、ALD技術の活用を是非多くの方にご検討いただければ幸いである。

<参考資料>

1)エレクトロニクス実装学会/すずウィスカ研究会編(2013)「高信 頼性鉛フリーめっきと錫ウィスカ対策」、日刊工業新聞社

2)Terho Kutilainen et al.,(2016)「Atomic Layer Deposition(ALD)to Mitigate Tin Whixker Growth and Corrosion Issues on Printed Circuit Board Assemblies」、

https://www.researchgate.net/publication/303999864_ Atomic_Layer_Deposition_ALD_to_Mitigate_Corrosion_ and_Tin_Whisker_Issues_of_Printed_Circuit_Board_ Assemblies(2019年5月21日アクセス確認)

3)八尋大輔(2019)「インプラント型電子メディカルデバイスへの ALD(原子層堆積)法による生体適合膜封止」、エレクトロニクス実装技術Vol.35 No.2