特集記事

設計・解析・シミュレーション ~ BGA実装不良の市場流出を防ぐ 「テスト容易化設計」の5つのポイント ~

アンドールシステムサポート(株)/谷口 正純、エスペック(株)/今堀 翔也

1. はじめに

世界スタンダードのJTAGテスト(IEEE1149.1規格 バウンダリスキャンテスト)は、高性能プロセッサ、組込み用マイコン、FPGA、PLD、DSPなどの半導体に標準で搭載されるようになった。

「JTAG(ジェイタグ)」は、一般的に開発現場で使われており、ソフトウェアエンジニアはArmマイコンのソフトウェア開発用 「JTAG ICE(デバッグプローブ)」が使われているし、ハードウェアエンジニアは「FPGAやフラッシュメモリの書き込み」のためにJTAGが使われている。

しかし、本来のJTAGの使い方は、デバッガや書き込み用のものではなく実装テスト用の標準規格である。

特にBGA部品を実装した基板においては、BGAの端子をバーチャルプローブとして使えるため、量産テストや試作基板のデバッグ、故障解析の場面で有効なテスト手法となる。

今後、DDR4メモリにはJTAGテスト用のコネクティビティテストモードが加わり、DDR5メモリはJTAGテストに対応することが決まり、JTAGテストを行う環境がさらに整うことになる。

JTAGテストの効果を企業全体で高めるには、設計段階でテスト容易化設計を考慮することが重要になる。

今回は製品のライフサイクルにおけるJTAGテストの活用例とテスト容易化設計の5つのポイントを紹介する。

2. JTAGテストの仕組み

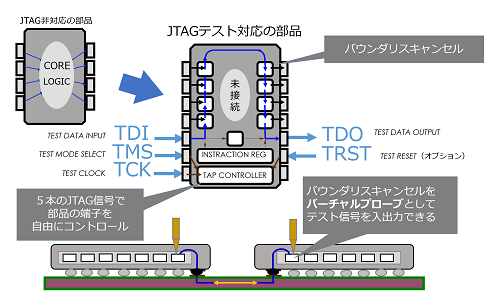

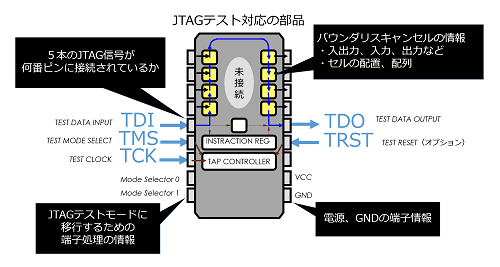

JTAGテストは、図1のように5本のJTAG信号(TDI、TDO、TMS、TCK、TRST(オプション))を利用して、JTAGテストに対応した部品をPCから自由にコントロールできる仕組みである。

図1 JTAGテストの仕組み

JTAG未対応の部品とJTAGテスト対応の部品を比較すると、部品がもつ本来のコアロジックと部品の端子の間に、バウンダリスキャンセル(Boundary Scan Cell)という信号を入出力させるためのロジックが追加されていることが分かる。

バウンダリは日本語で「境界」という意味であり、コアロジックと部品の端子の境界をスキャンできることを意味している。

このようにJTAGテストとは、バウンダリスキャンセルを制御して、部品の端子をバーチャルプローブとして通電試験ができるテスト手法である。

テスト中はJTAGテスト対応部品のコアロジックが切り離され、部品の端子から自由に信号を入出力することができる。

そのため、JTAGテストのメリットは、マイコンのプログラム開発やFPGAのロジック開発をせずに基板のテストができることである。

このテストの仕組みは、皆さまが使用している主要部品に予め内蔵しており、多ピンのFPGAやマイコンを搭載したBGA基板のデバッグ効率をあげることができる。

JTAGテストによって見つけられるBGA基板の不具合には、「はんだ不良(オープン不良、ブリッジ不良)」、「プリント基板のパターン不良(断線、ブリッジ)」、「部品内部のボンディングワイヤの断線」、「部品の型番違い」、「実装方向のミス」などがある。

JTAGテストは、測定器ではプロービングできない不良を検出できることから、近年の高密度実装基板に対する有効なテスト手法の1つとなっている。

試作基板の受入検査でJTAGテストを活用することにより、モノづくりに問題がないことを確認した上で、設計のデバッグに注力でき、開発期間を短縮できた事例もある。

また、国内では量産テストの導入事例が多くあり、JTAGテストを活用することにより、BGA実装不良品を市場に流出さない取り組みで使われている。

3. JTAGテストツール『JTAG ProVision』とCR-8000 『Design Gateway』の連携

JTAGテストの規格が誕生した1990年から約15年間は、JTAGテストツールが成熟しておらず、JTAGテストアプリケーションを準備するためには、ユーザーがテスト対象の回路図を読み解きながら、テキストエディタを使用して手作業でテストアプリケーションを作り込む必要があった。

テストアプリケーションを作るためには、回路設計者と同等に回路を理解することが求められ、JTAGテストを導入した企業では、専任の技術者を育成する必要があった。

そのため、JTAGテストを導入したものの、継続して使っていくことが困難な時代もあった。

しかし、この状況はJTAGテストツールの進化により一変した。

オランダのJTAG Technologies社が2005年にリリースしたJTAGテスト統合環境『JTAG ProVision』がリリースされ、テストアプリケーションの自動生成機能が大きく進化した。

誰でも簡単にJTAGテストアプリケーションを自動生成できるようになり、製造現場で継続して利用できる環境が整った。

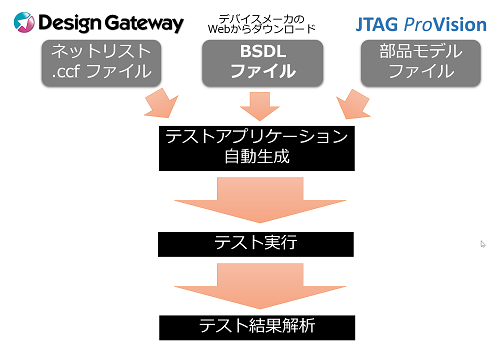

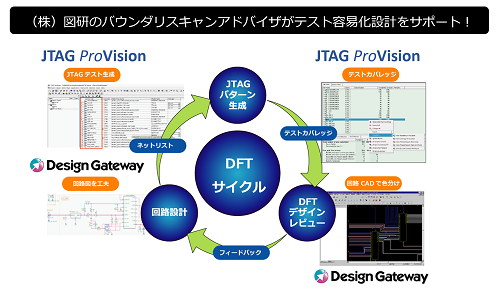

さらに図2のように、(株)図研のCR-8000『Design Gateway』の回路図CADと連携できるようになり、回路設計者の方にも使いやすく進化した。

図2 JTAG ProVisionとDesign Gatewayの連携

4. テストアプリケーション生成に必要なファイル

JTAG ProVisionを使ってJTAGテストアプリケーションを生成するためには、図3のように基板を製造するために使用するネットリスト 「.ccfファイル」(回路CAD 『Design Gateway』)から生成される配線情報)とJTAG対応部品のテスト回路情報が記載されている「BSDLファイル」(デバイスメーカーより提供されるJTAG対応部品のファイル)、JTAG非対応部品の「部品モデルファイル」(JTAG ProVisionに内蔵されている部品のロジックデータ)からテストアプリケーションが自動生成される。

図3 JTAGテスト自動生成の仕組み

BSDLファイル(Boundary Scan Description Language)とは、JTAG対応部品にどのようなバウンダリスキャン用の回路が内蔵されているか記載したものである。

このBSDLファイルには、JTAG対応部品のバウンダリスキャンセルをコントロールするための情報が記載されており、JTAGテストを実行する際には必須となる重要なファイルである。

5. JTAGテストによるBGA基板のテストカバレッジ

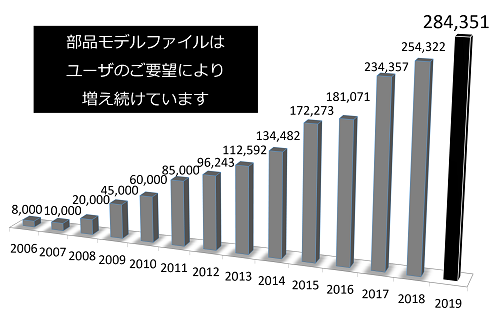

JTAGテストによるテストカバレッジは、JTAG ProVisionの部品モデルファイルの部品情報を元に自動生成されるため、準備されている部品モデルの種類が重要となる。

JTAG ProVisionには、図4のように2020年5月末の時点で28万種類の部品モデルファイルが用意されている。

図4 部品モデルファイルの推移

多くの場合は、製品に付属している部品モデルで十分であるが、部品モデルファイルがない場合には、メーカーで部品モデルを作成するサービスがある。

データシートのPDFファイルをメーカーに送付すると、3日ほどで新しい部品モデルファイルが提供される。

もし、機密情報が含まれる部品の場合には、ユーザーが部品モデルファイルを生成するためのツールも標準で用意されている。

この部品モデルファイルには、部品のピン情報、信号の入出力属性、出力される期待値の情報が含まれている。

検査対象の基板に対して、どのようなテストアプリケーションが自動生成されるかを図5に示す。

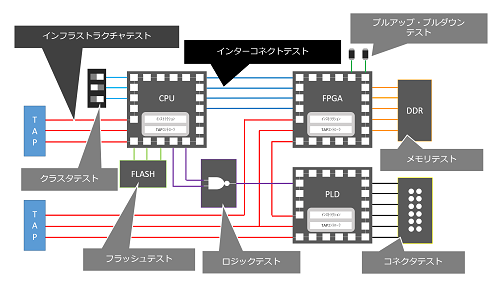

図5 基板全体をテストできるJTAGテスト

「インフラストラクチャテスト」は、基板に正しく通電されているか、JTAG信号に不良がないか、正しい部品が実装されているかを、JTAG対応部品のID番号を照合してテストすることができる。

このテストに問題が無ければ、JTAGテストを実行するためのインフラが準備できたことになる。

次に実行するのは、JTAGテストのメインである「インターコネクトテスト」である。

JTAGテスト対応部品間の配線とはんだ不良の有無をテストできる。

その他のテストは、JTAGテスト非対応の部品をテストするもので、「プルアップ・プルダウンテスト」「メモリテスト」「コネクタテスト」「ロジックテスト」「フラッシュテスト」「クラスタテスト」などがある。

以前からJTAGテストを知っていた方の中には、JTAG対応部品間のインターコネクトテストしか出来ないと誤解されている方も多いようである。

現在は、JTAGテストツールの進化により、国内のお客様の事例で画像処理用の基板において、85%のテストカバレッジが得られた例もあった。このようにJTAGテストのテストカバレッジは、劇的に向上していることが分かる。

6. テスト容易化設計で注意すべき5つのポイント

JTAGテストの効果を最大限高めるためには、モノづくりをする前の回路設計段階に、これからご紹介するテスト容易化設計で注意すべき5つのポイントを考慮することをお勧めする。

回路設計や基板設計に大きな負担はなく、もしBGA実装不良で困ったときにJTAGテストがトラブル解決の糸口になるはずである。

■ポイント1......「主要部品選定時にBSDLファイルを入手する」

マイコン、プロセッサ、FPGAなどの主要部品を検討する際には、JTAG対応部品(バウンダリスキャン対応部品)を選定することがもっとも重要である。

JTAGテストに対応した部品であれば、BSDLファイルを入手できる。

同じ性能の部品であれば、JTAG対応部品を選ぶことでバーチャルプローブとして実装府品を使うことができるようになる。

部品の価格も数ピン増えるだけでは大きく変わらず、開発、製造、保守、故障解析などのシーンでテストと故障解析能力が大きく変わってくるため、トータルのコストは考えるまでもない。

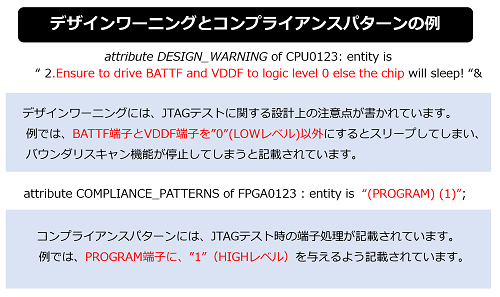

BSDLファイルには、図6のように部品のピン情報、 バウンダリスキャン命令のコードやセルの配置等について記載されており、マイコン、FPGAなどの部品メーカーから入手できる。

また、JTAGテストモードに移行するための端子処理について記載されている。

図6 BSDLファイルに記述されている情報

もし、BSDLファイルがホームページに公開されていない場合には、部品の販売代理店にお問い合わせいただくと入手できることがある。

JTAG対応部品であるか調べるときには、BSDLファイルを探すことから始めていただきたい。

■ポイント2......「回路設計上の注意点に気を付ける」

JTAGテストを行うためには、部品をJTAGテストモード(バウンダリスキャンモード)に移行するための端子処理が必要な場合がある。

端子処理の有無を確認するためには、はじめにデータシートを確認する必要があるが、膨大なデータシートの中から必要な情報を探し出すのは大変な作業である。

そのため、次に挙げるキーワード「JTAG」「バウンダリスキャン(Boundary-Scan)」「IEEE1149.1」を検索するとよい。

これでも情報が見つからない場合には、JTAG信号「TDI」「TDO」「TCK」「TMS」「TRST」で検索すると注意点が記載されていることがある。

次に、図7のサンプルに示すBSDLファイルに記述されている設計上の注意点を確認する必要がある。

図7 BSDLファイルの例

BSDLファイルはテキストファイルになっており、ダウンロードしたBSDLファイルをテキストエディタで開いていただきたい。

注目するのは、設計上の注意点「attribute DESIGN_WARNING」とコンプライアンスパターン「attribute COMPLIANCE_PATTERNS」というキーワードである。

世界スタンダードのIEEE1149.1で定められたキーワードになっている。

また、コメント文にも注意事項が含まれているケースもあるので、「IMPORTANT NOTICE」というキーワードなどにも注目するとよい。

■ポイント3......「JTAG信号の基本回路をチェックする」

もし、製造不良が起きたときに、基板をデバッグしようと思っても、JTAG信号が未使用ピンとしてGNDに短絡されていると、せっかく主要部品がもっているJTAGテスト機能を活かすことができない。

特にBGA部品のJTAG信号は、回路設計と基板のレイアウト設計時にJTAG信号をアクセスできるように考慮することが重要である。

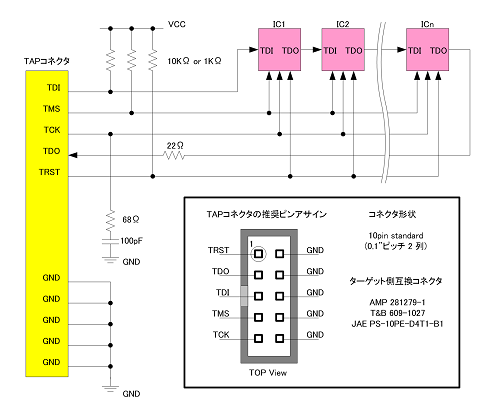

JTAGの5本の信号(TDI、TMS、TCK、TDO、TRST(オプション))をアクセスできるか確認していただきたい。

図8の参考回路で示すように、JTAGテストの動作を安定させるため、GNDを複数ピンアクセスできるようにして、終端処理をすることを推奨している。

終端回路は、部品メーカー推奨のJTAG回路がデータシートに記載されているが、特に指定がない場合には、図8のJTAGテストツールの推奨回路を参考にしていただきたい。

図8 JTAG信号の基本回路

TAPコネクタは、JTAGコントローラを接続するためのコネクタである。

コネクタのスペースがない場合や量産製品でコネクタを未実装にする場合には、テストパッドを設けておく方法がある。

量産時には、ピン治具からJTAG信号のテストパッドからJTAGテストを行うことができるし、試作時には、テストパッドにケーブルをはんだ付けして、実装テストや故障解析を行うことができる。

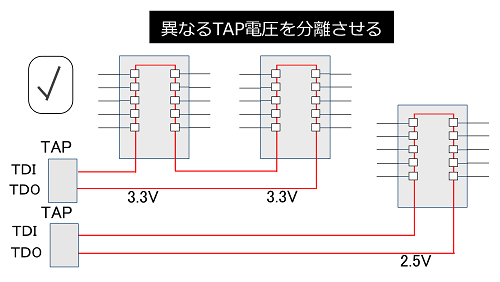

■ポイント4......「JTAGチェーンの回路をチェックする」

複数のJTAG対応部品を同時に制御するために、JTAG信号をシリアル接続することをJTAGチェーン接続と呼ばれている。

シリアル接続する際には、図9のようにTDIとTDOの入出力属性に注意が必要である。

図9 JTAGチェーンの回路例

また、電圧レベルが異なる部品を同じチェーンにしてしまうと、回路が正しく動作しないため、電圧レベルが異なる部品は、JTAGチェーンを分離する必要がある。

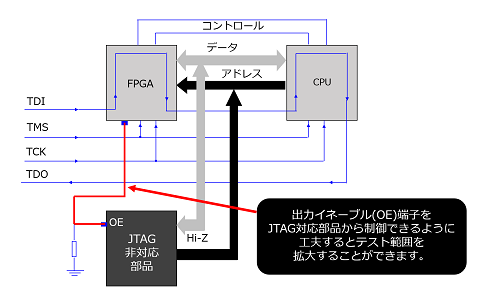

■ポイント5......「JTAGの非同期回路を制御する」

JTAGテストは、図10のように複数のJTAGテスト対応部品のテストクロック(TCK)を使って、同期をとりながら信号の入出力をさせてテストする仕組みである。

図10 非同期回路の工夫によるテストカバレッジの拡大

FPGAとCPU間のデータバスとアドレスバスのテストを行うときに、JTAG非対応部品から出力してしまうと出力信号が競合してしまいテストできなくなってしまう。

そこで、JTAGテスト範囲を拡大するには、出力競合を抑える回路が必要となる。

この場合、JTAG対応部品からJTAG非対応部品の出力イネーブルを制御できるようにするとテストカバレッジを拡大することができる。

7. テストカバレッジの評価方法

ご紹介した5つのポイントをおさえれば、JTAGテストを行う下準備が整ったことになる。

JTAGテストのテストカバレッジを評価するためには、手作業でBSDLファイルの内容を確認しながら回路図にマーキングする方法があるが、最近のJTAGテストツールでは、テストアプリケーションが自動生成されるため、実際にテストパターンを生成した方が簡単かつ詳細にテストカバレッジを確認できる。

図11は、回路CAD『Design Gateway』を使用した例であるが、回路設計が終わるとCADから基板設計するためのネットリスト(ccfファイル)を出力できる。

図11 DFTデザインレビューによる改善サイクル

このデータをJTAG統合環境『JTAG ProVision』にインポートして、テストパターンを自動生成する。

次に『JTAG ProVision』のテストカバレッジ検証ツールを使い、生成したテストパターンが、部品番号、ピン番号、ネット名に対してテストできているか結果が表示される。

このテストカバレッジの結果を回路CADにインポートすると、「Design Gateway」の回路図上にテストカバレッジの情報がマーキングされる。

回路設計者は、テストカバレッジの情報がマーキングされた回路図を使って、デザインレビューを行うことができる。

このデザインレビューは、「テスト容易化設計 DFTデザインレビュー」と呼んでおり、製品の性能実現や製造コストのためだけのデザインレビューだけではなく、製造時のテストを考慮したデザインレビューを実現できるようになる。

DFTデザインレビューの結果、テストカバレッジが低い場合には、基板製造前に回路を工夫することでテストカバレッジを改善することができる。

具体的な対策としては、ピンアサインの変更、未使用ピンの利用、部品の変更など様々な方法がある。

回路変更後は、修正した回路図からネットリストを出力して、『JTAG ProVision』に読み込むと、回路変更した結果に対応したJTAGテストパターンをすぐに生成できる。

さらに、回路図に検査治具や検査装置の回路図を含めることで、量産を意識したDFTレビューを行うことができる。

このDFTデザインレビューと回路変更のサイクルを繰り返すことにより、基板製造前に品質向上と検査コスト削減、開発期間短縮による開発コストの削減を確実に実現することができる。

特にプローブピンを使用できない高密度な基板においては、DFTとテストカバレッジのレビューが製品のライフサイクルにおける品質向上とコスト削減、直行率の改善を成功させるポイントになる。

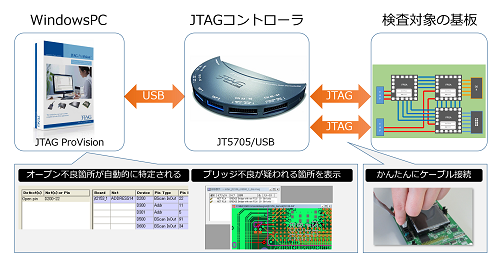

8. 回路設計者のDFTのメリット

回路設計者がテスト容易化設計に配慮して試作基板を製造すると、試作基板の受入検査で図12のように手軽に、実装不良の有無を確認することができる。

図12 JTAGテストの実行イメージ

したがって、回路のデバッグを物理的な不良がない基板で進められるため、デバッグ期間を短縮することができる。

通常、回路設計者は周辺回路を動かすためのソフトウエアやFPGAのロジックが必要であるが、JTAGテスト対応部品のバーチャルプローブをパソコンから自由自在に制御できるため、周辺回路のデバッグを回路設計者のみで容易に進めることができる。

また、周辺回路に対するテストアプリケーションが部品ライブラリから自動生成されるため、回路設計ミスに気づきやすいというメリットもある。

受け入れ検査で使用したJTAGテストアプリケーションは、量産検査としても使用できるため、量産テストの準備にかかる工数を削減できる。

特にファンクションテストを設計者が開発している企業にとっては、ファンクションテストの規模を大幅に縮小できることになり、本業である新製品のソフトウェア開発に注力できる。

さらに製造不良の故障解析を設計者が担当する企業では、JTAGテストにより故障解析を自動化できるため、設計者の負担を低減することができる。

9. JTAGテストを導入した理由とメリット

JTAGテスト導入後の製造現場のメリットは、BGA実装基板を多く扱っている企業ほど大きくなる。

当社のJTAGテスト導入企業からは「BGAのはんだオープン、はんだショートなどの実装不良を確実に検出できた」「不良箇所が自動診断されるため、修理時間が圧倒的に短縮できた」「BGAや極小部品は目視での確認ができないため将来の実装基板検査にはJTAGテストが必須になる」という声をいただくことが多い。

インサーキットテストを実施している企業がJTAGテストを導入した理由は、基板が高密度化するなかでBGA部品が増えてプローブピンが当たれなくなったり、テストパッドを配置することが困難になったり、複雑な基板ではプローブピンが1000ピンを超えたために直行率が低下してしまったり、プローブに関する課題を改善する目的である。

JTAGテストを単独で実施することもできるが、抵抗値などの定数はテストできないため、インサーキットテストと組み合わせてテストすることにより、検査機の長所を組み合わせてテストカバレッジを最大化することができる。

また、ファンクションテストを実施している企業では、製品の高性能化に伴いプログラムの開発規模が増大している課題があり、ファンクションテストの開発負荷を低減するためにJTAGテストとファンクションテストを組み合わせて導入する企業が増えている。

ソフトウェア設計者の貴重なリソースを製品のプログラム開発に注力することができるため、製品の開発サイクルを短縮できるようになる。

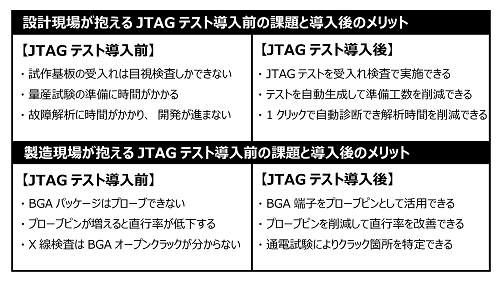

JTAGテストは製造現場のみにメリットがあると思われることが多いが、図13のように設計者にとってもメリットが大きいことをお分かりいただけたのではないだろうか。

図13 JTAGテストによる設計現場と製造現場のメリット

新製品の開発サイクルを早めるためには、設計者の負担を少しでも減らして、製品開発に集中できる環境を整えることが重要であり、JTAGテストの活用により、新製品の開発サイクルを短縮することが企業にとって大きなメリットとなる。

10. まとめ

JTAGテストを導入して成功している企業では、製品の設計段階で「テスト容易化設計DFT」を実践することをルール化しており、デザインレビューの項目の1つに「DFT」というキーワードを挙げて取り組まれている。

最大限にJTAGテストを活用できる環境が整うと「BGA実装不良基板の市場流出防止」だけではなく、「開発期間の短縮」「検査準備の工数削減」「検査時間の短縮」「故障解析の工数削減」「製品品質の向上」など、設計から製造、保守までの全ての製品ライフサイクルでメリットが得られる。

したがって、試作基板の設計段階からDFTを実践することが、企業全体の利益に直結することがわかる。

現在、当社ではJTAGテストに関するWebセミナー「JTAGテスト入門セミナー」「JTAGテスト成功事例セミナー」「JTAGテスト成功事例セミナー」などを無料で開催しているので、参考にしていただけると幸いである(https://www.andor.jp/jtag/jtag-webinar/)。