特集記事

半導体業界の話題(第2回) 〜エレクトロニクス業界の発展を牽引してきた「ムーアの法則」はさらに続く〜

厚木エレクトロニクス 加藤 俊夫

1. ムーアの法則とは何か

今から52年も前に、インテル社のゴードン・ムーア氏が、「半導体の集積密度は、1年で2倍になる」という予測を雑誌に掲載したのが「ムーアの法則」となった。1965年にはシリコンチップ1つに60個載っていたトランジスタは、1975年には65000個がチップに載ると仮定すると、1年で2倍の集積度になると予言した訳である。インテルが「4004」CPUを作ったのは1970年のことであり、1965年にはプロセッサという概念すらなかった時代で、その時のチップサイズは2Mil平方、メタル配線は2層、ウエファーは1インチ(25mmφ)であった。ムーア氏については、2月号のインテル(株)の紹介に載せたのでここでは省略する。

その後もムーアの法則は続き、1980年代にはDRAMが集積度向上の主役となり、1Mbitは、3年後に4Mbit、6年後に16Mbit、9年後に64Mbitといった調子で、3年で4倍のペースで進展し、ムーア氏が予言した集積度が年々向上すると言う思想は現在も依然として続いている。

最近の10数年間のパターン微細化は、90nm→65nm→45nm→32nm→22nm→14nm→10nmという調子で進行しており、トランジスタが微細化されるとチップ面積あたりのトランジスタ数が増えるので、LSIの集積度がどんどん向上している。

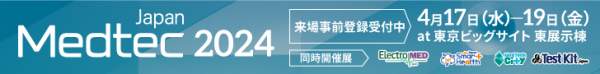

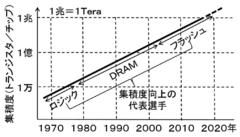

さらに微細化だけでなく、縦方向に3次元的に積むデバイスも現れて、集積度の向上は加速されている。図1は、DRAMやフラッシュ・メモリの集積度の変遷を表したグラフで、実に縦軸は4桁単位で表される急激な進歩で、こんな桁違いに上昇するような産業は他にないであろう(HDDは、LSIに対抗するように向上しているが)。本年はついに1チップ上に1Terabit(1012bit、1兆ビット)のNANDフラッシュメモリが実現する可能性がある。しかし、微細化がいつまでも続くはずがなく、「ムーアの終焉」が心配されている。果たして進歩は止まるのか? 今月から数回にわたって議論しよう。

図1 LSIの集積度/チップの変遷

2. CMOSとインバータについて簡単な解説

LSIの基本となるCMOSについては、皆様は十分お馴染みと思われるが、念のため最初に説明しておく。

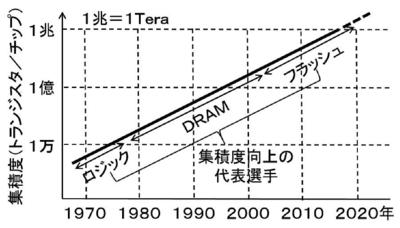

まずNMOSは、P型のWellにイオン注入でN型のソースとドレインを形成し、薄い酸化膜を挟んでゲート電極を設けた構造で、PMOSはこれと逆に、N型WellにP型のソースとドレイン及びゲートを設けたもので、図2に構造図を示す。NMOSのゲート電極にプラスの電圧を与えると、ゲート下のチャンネル層にマイナスの電荷が誘起され、N型のソースとドレイン間が導通してON状態になり、ゲートにマイナスの電圧が与えられると導通せずOFF状態になる。PMOSはこれと逆で、ゲートにマイナス電圧が与えられるとONとなり、プラス電圧だとOFFとなる。

CMOS(Complementary Metal Oxide Semiconductor)は、同一シリコンチップ上にNMOSとPMOSを作りこんだもので、上図のような構造になる

図2 CMOS構造の断面図

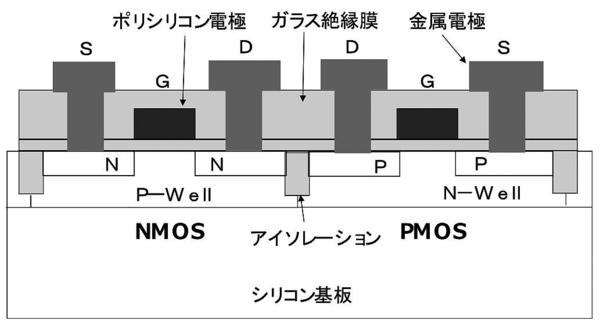

さて、このようにNMOSとPMOSを隣同士に並べて作り込んだのは、図3のようなインバータ回路を作るためで、NMOSとPMOSのゲート同士、ソース同士を近接させて、それらを接続する。

図3 インバータ回路

この回路で、入力にプラスの電圧が与えられると、NMOSはON、PMOSはOFFとなるので、出力は−Vにつながる。入力がマイナス電圧だと、NMOSはOFF、PMOSはONとなって出力は+Vになる。すなわち、入力がプラスなら出力はマイナス、入力がマイナスなら出力はプラスに反転するわけで、このような回路をインバータといって、LSIの基本となっている。

LSIの集積度がどんどん大きくなるのは、このようなNMOSとPMOSのペアが、小指の爪程度の小さい面積のチップ上に数百億ペアも載っているわけである。

3. ムーアの法則を実現した微細化の進展

IBMのロバート・デナード氏は、1974年にMOSトランジスタの比例縮小則(Scaling Rule)を発表し、微細化により性能が上がり集積度が増すことを示した。この比例縮小則が指導原理となって、微細化競争が50年近く続いている。

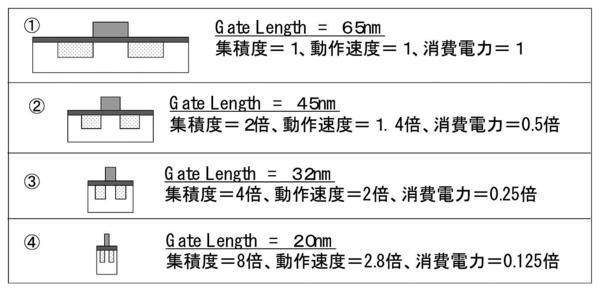

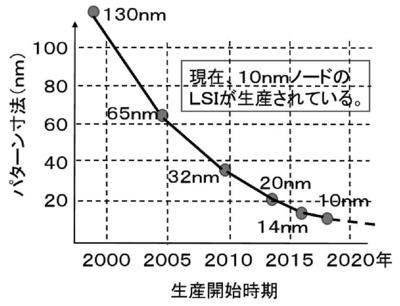

これによると、「トランジスタのパターン寸法を仮に0.7倍に縮小すると、集積度は2倍、動作速度は1.4倍、消費電力は1/2となり、図4のように微細化の世代ごとに集積度も性能も向上し、微細化して悪いことはなにもない。このため業界を挙げて微細化競争となり、21世紀になってパターン寸法はナノメーターになり、今や図5のように10nmのCMOSLSIが生産され、更に5nmや3nmを開発するという声も聞こえている。まさに「ムーアの法則」がますます進んでいるといえる。

図4 比例縮小則で、MOSトランジスタが縮小される様子

図5 LSI微細化の経過と今後の予測

4. 微細化に伴う問題点

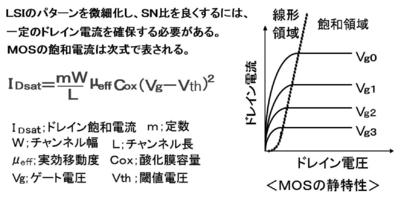

MOSトランジスタの寸法を微細化することにより、性能も集積度も向上してきたが、微細になると駆動電流(IDSAT)を大きくとることが難しくなってきた。駆動電流は、図6の式で表され、これを大きくするには、チャンネル幅(W)を大きく、実効的移動度(μeff)を大きく、酸化膜容量(COX)を大きく、ゲート電圧(Vg)を大きく、チャンネル長(L)を小さくすれば良いことが式から読み取れ、このため涙ぐましい努力が行われている。

図6 MOSの駆動電流の式と静特性グラフ

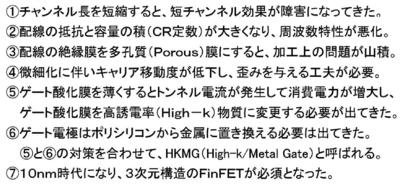

順調に微細化が進んでいたCMOSLSIも、2000年ごろの100nm付近を境にして、単にパターンを微細化するだけでは性能の向上が図れなくなり、多くの弊害があらわれるようになった。

代表的な問題点を表1に列記したが、それぞれについて次号で詳細を取り上げる。

表1 CMOSLSIの微細化に伴い発生した諸問題